Electrical Specification

Backplane Topology

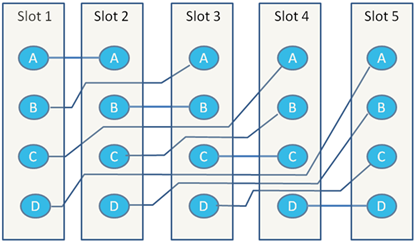

The backplane is a key element in achieving high-speed connections between the plug-in modules or nodes in the case of a JAS system. VPX compliant backplanes support a minimum signaling rate of at least 3.125 Gbps on any differential point-to-point connection. There are a small number of required signals on the backplane including power, reference clock, JTAG, system controller, and system reset. In addition the specification details a recommended set of pin mappings between the plug-in module wafer signals and the backplane slots for the single-ended, differential and power types of connectors. For example, a recommended mapping for the differential pairs of a serial communications protocol in a five slot full mesh backplane is illustrated below. When routed in this manner the nodes can be plugged into any slot and still have communications with the nodes in all other slots.

Recommended backplane routing for a 5-slot full-mesh connection

ANSI/VITA 46.0_2013

"VPX: Base Specification". ANSI/VITA 46.0, 2007 (R2013), VITA Technologies (VITA), 2013.