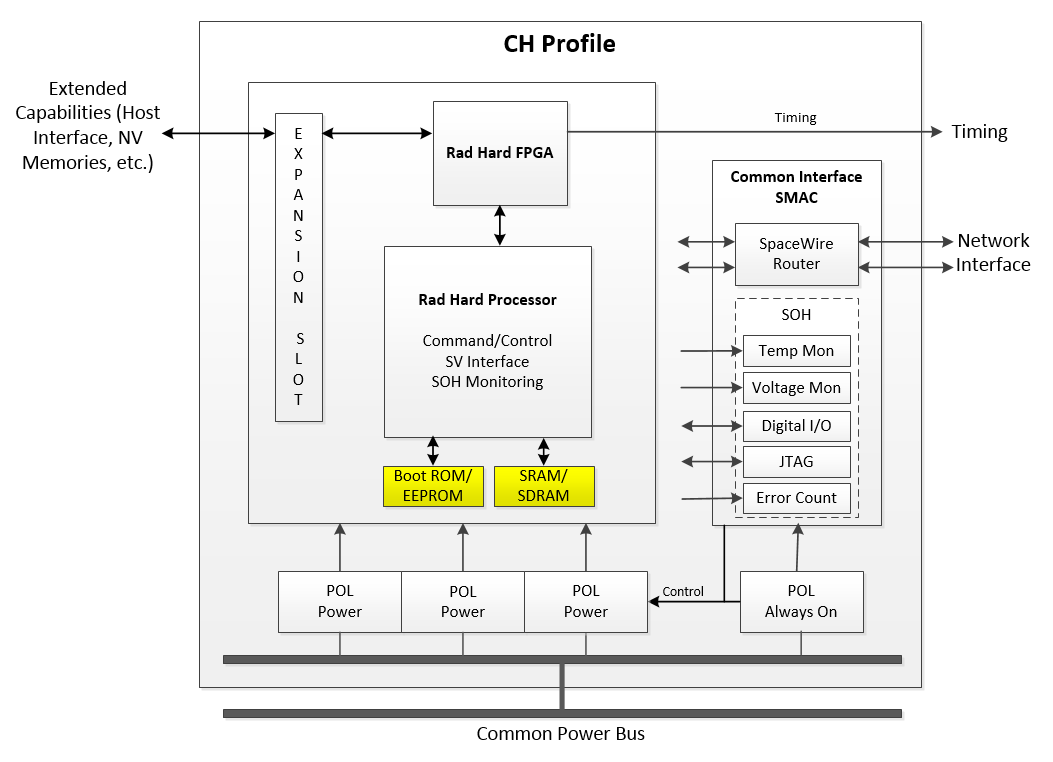

Command and Host Processor Profile

Memory Technologies

There are two types of memory technologies that are highly recommended for inclusion on the CH node: non-volatile flash or EEPROM, and higher-speed SRAM or SDRAM memory.

Non-volatile memory is necessary to store the software that the microprocessor will execute upon power-up. Non-volatile memory may also be necessary to store the firmware for any SRAM-based FPGAs on the CH node or other nodes. This can be implemented through a variety of technologies, but must ultimately be compatible with the memory interface on the microprocessor device and the FPGA. The amount of storage needed will depend on the functionality required by the application, the number and size of SRAM-based FPGAs, and redundancy requirements.

A second memory type, usually SRAM or SDRAM, may provide code, stack, and heap storage for software executing on the microprocessor. The amount of storage needed will depend on the complexity of the software being executed. Again, the memory technology must be compatible with the interfaces available on the microprocessor device.

Note that if it is desired to use memory technologies that are not supported by the microprocessor, it may be possible to attach the memory technologies to the companion FPGA instead, and implement a memory controller in the FPGA logic that would translate memory requests into memory transactions on the unsupported device.

CH Node Memory Technologies