System Monitoring and Communication Profile

Processing Logic

Domain(s)

Space

System(s)

Satellite

Profile(s)

SMAC

SMAC Processing Logic

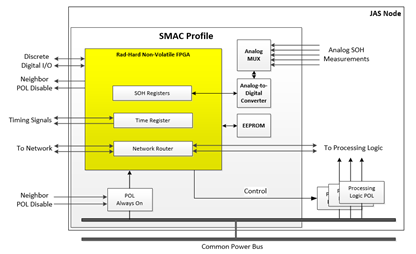

The SMAC utilizes a radiation-hardened, non-volatile FPGA device to provide the primary processing capability for SMAC functions. This FPGA shall always be powered on when system power is applied regardless of the power state of the remainder of the node. It is recommended to use local POL power conversion to power the FPGA when system power is applied.

The FPGA logic should have the following functional interfaces:

| Functional Category | Target | Purpose |

| Network Router | Off-board connector (through external transceivers if necessary) | Provide network connectivity to the node |

| Analog SOH | Analog-to-Digital converter | Measures a SOH value (temperature, voltage, current) |

| Analog SOH | Analog multiplexer | Select a channel for ADC to record |

| Discrete I/O | Node processing electronics | Provide discrete I/O and data bus interfaces to node processing electronics (for example, to have a network-enabled CPU reset for a CH node) |

| Node control | Local POL regulators | Control power enables for node electronics |

| Node control | Neighboring node POL regulators | Provide the ability to remove all power (including SMAC) from a neighboring node |

| Personality | NV Memory | Read startup configuration and node personality information |

| Timing | Node processing electronics | Provide timing pulse for system time synchronization |

SMAC Functional Interfaces