System Monitoring and Communication Profile

Functional Description

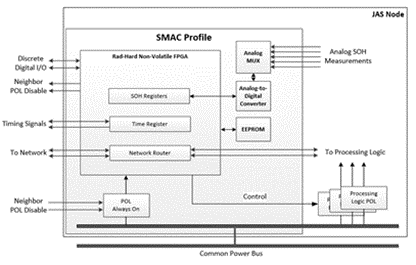

The SMAC is responsible for enabling the following capabilities on JAS nodes:

- Network (typically SpaceWire) router for command and control

- Control to read and drive discrete digital I/O and data buses

- Configuration of node FPGA(s)

- SOH reporting, including node temperatures, voltages, and currents

- Local and neighboring node power control

- Connectivity to personality NV memory

- System timing synchronization

One important characteristic of the SMAC is that it shall be powered up whenever system power is enabled, even if the remainder of the node remains powered down. This is to enable network connectivity and provide proper reporting of SOH regardless of the state of the node’s processing logic.

The recommended approach is to implement SMAC capabilities using a radiation-hardened and non-volatile Field Programmable Gate Array (FPGA) as the main processing technology. If other processing technologies are used instead, the replacement technology should be radiation-hardened to avoid potential system downtime from network failure caused by single-event effects. An FPGA with non-volatile configuration is also desired to simplify the initialization of the SMAC. The SMAC functionality can also be integrated within the main processing logic element or as part of the software implementation if needed.

The FPGA logic implements control logic to drive external components that realize the SMAC functionality. Some of these other components include an Analog-to-Digital Converter (ADC) and analog multiplexer (MUX) for reading SOH, LVDS transceivers for SpaceWire signaling, and an external NV memory to hold personality information and power-up configuration.

A block diagram of the SMAC node is shown below:

Profile Block Diagram