Command and Host Processor Profile

Companion Field Programmable Gate Array

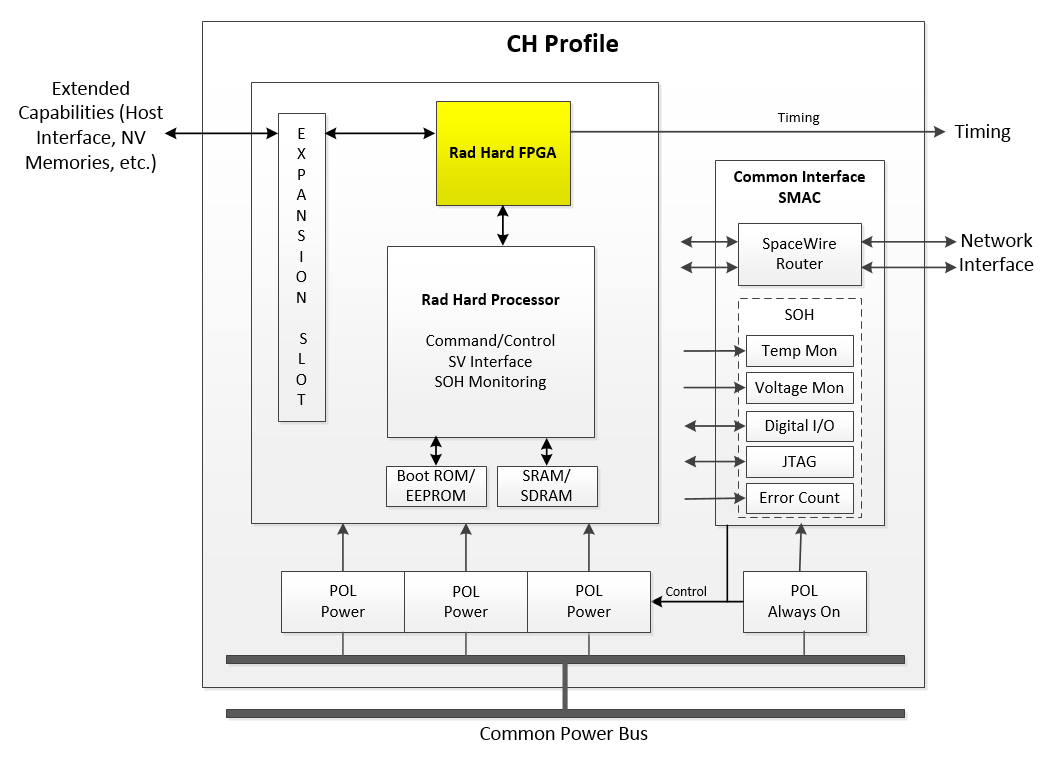

A separate radiation-hardened companion FPGA is present on the CH node to implement timing functions, custom peripherals, and bridge to proprietary interfaces that may not be directly supported by the microprocessor. The FPGA typically attaches to the microprocessor through industry-standard bus interfaces, though the exact connection method will vary based on the selection of microprocessor hardware.

Because of the flexibility of an FPGA, its logic can be customized to attach to a variety of interfaces, thus forming a configurable bridge between the processor and electronics not natively supported by the microprocessor hardware. Most commonly, this is used to connect spacecraft interfaces (using protocols not typically seen in a JAS system, such as MIL-STD-1553) to the payload. An example of this instantiation in a system is given in the Applications section of this profile.

The FPGA can also implement peripherals that can offload microprocessor workload by performing various system functions. The most common example of this is timing synchronization for nodes; the FPGA can provide a timing pulse for the system, saving the microprocessor from interrupt execution at every time epoch.

It is highly recommended that the companion FPGA be a radiation-hardened device for reliability purposes.

CH Node Companion Field-Programmable Gate Array