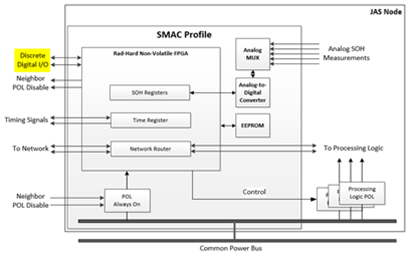

System Monitoring and Communication Profile

Discrete Signaling

SMAC Discrete I/O and Data Bus Signaling

The SMAC has capabilities to read and drive both discrete I/O values and data buses. The FPGA I/O dedicated for this purpose can be either configured as dedicated inputs and outputs or can be bi-directional with input or output behavior configured through the network.

Driving data buses can enable the configuration of SRAM-based FPGAs across the network, allowing a system controller to distribute tasks across networked nodes as dictated by mission needs. This is also a key factor in establishing an M-of-N redundancy scheme with respect to node hardware, which is one of the JAS architecture’s primary benefits.

Discrete I/O can be used to drive control signals or to return discrete states back to the system controller as SOH. Possibilities for these signals include driving a node reset line or connecting to a device’s JTAG port to enable built-in self-test capabilities. The processing element can also drive some of these signals in order to report back information needed in the node SOH (for example, error flags or network link status).